« SE4Binome2025-2 » : différence entre les versions

Aller à la navigation

Aller à la recherche

Aucun résumé des modifications |

Aucun résumé des modifications |

||

| Ligne 28 : | Ligne 28 : | ||

=== Schématique === | === Schématique === | ||

</syntaxhighlight>[[Fichier:Schema carte mere.jpg|gauche|vignette|500x500px|Schéma carte mère du pico ordinateur]] | </syntaxhighlight>[[Fichier:Schema carte mere.jpg|gauche|vignette|500x500px|Schéma carte mère du pico ordinateur]] | ||

Version du 10 novembre 2025 à 09:34

Objectif

L'objectif du projet est de concevoir un pico-ordinateur complet, intégrant :

- Une carte mère basée sue le microcontrôleur AT90USB1286

Une partie logicielle permettant l'éxecution de de commandes telles que ls, cp ou mv

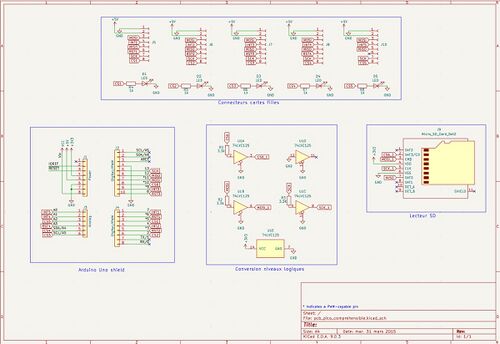

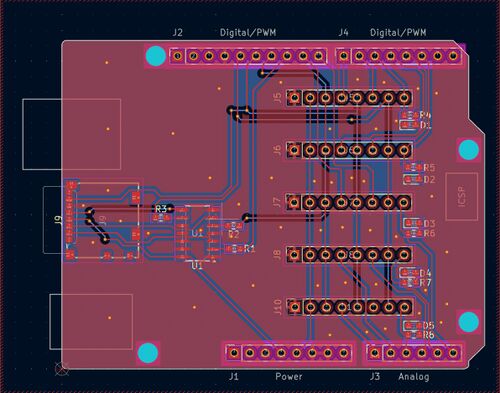

Shield Arduino

Une première étape du projet a consisté à développer un shield pour Aduino uno, servant de plateforme de test et de développement pour les cartes filles SPI.

Fonctionalités:

- Connexion de 5 périphériques SPI via des cartes filles.

- Gestion des signaux Reset et Interruption.

- Ajout d'une mémoire externe carte micro-SD via un connecteur Molex 10431.

- Adaptation des niveaux logiques (5V a 3,3V) grâce à la puce 74LV125.

Ce shield joue le rôle de plateforme de développement temporaire, en attendant la carte mère du pico-ordinateur.

Schématique et routage

Objectif

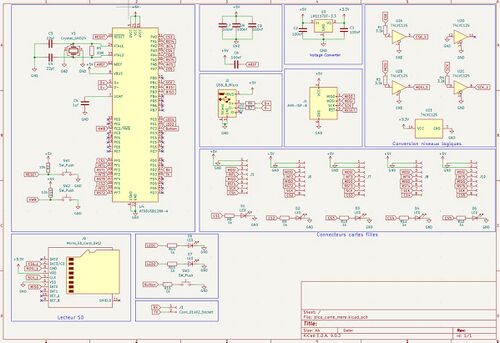

Carte mère

Schématique

</syntaxhighlight>