SE4Binome2025-2

Objectif

L'objectif du projet est de concevoir un pico-ordinateur complet, intégrant :

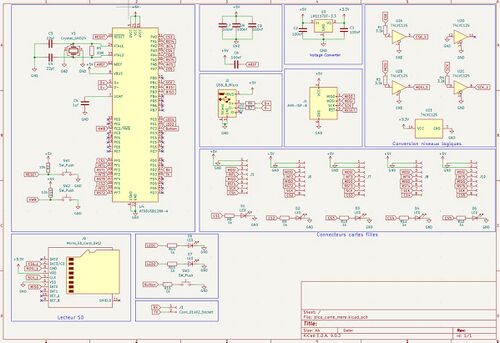

- Une carte mère basée sue le microcontrôleur AT90USB1286

Une partie logicielle permettant l'éxecution de de commandes telles que ls, cp ou mv

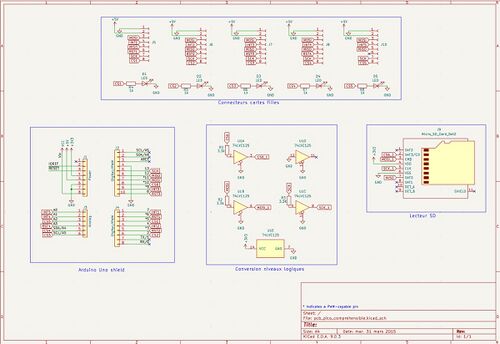

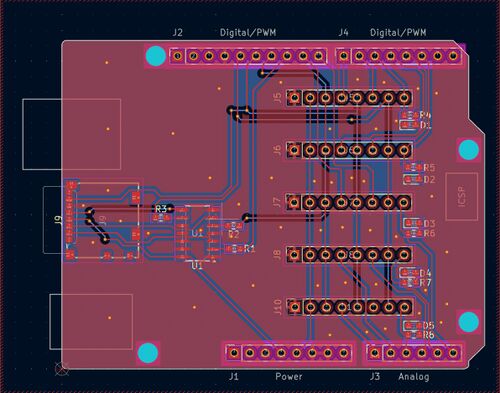

Shield Arduino

Une première étape du projet a consisté à développer un shield pour Aduino uno, servant de plateforme de test et de développement pour les cartes filles SPI.

Fonctionalités:

- Connexion de 5 périphériques SPI via des cartes filles.

- Gestion des signaux Reset et Interruption.

- Ajout d'une mémoire externe carte micro-SD via un connecteur Molex 10431.

- Adaptation des niveaux logiques (5V a 3,3V) grâce à la puce 74LV125.

Ce shield joue le rôle de plateforme de développement temporaire, en attendant la carte mère du pico-ordinateur.

Schématique et routage

Objectif

Carte mère

Schématique

Firmware: RTOS

Architecture Report

1 System Architecture Overview

The firmware implements a cooperative real-time operating system (RTOS) for AT-

mega328p microcontrollers, featuring a memory-optimized kernel with round-robin schedul-

ing capabilities.

1.1 Component Hierarchy

firmware/

kernel/

kernel.[ch] - Core kernel management

scheduler.[ch] - Task scheduler implementation

task.[ch] - Task control block system

config.h - Resource configuration

main.c- Application layer

2 Core Kernel Mechanisms

2.1 Task Management System

The kernel implements a static task control block (TCB) architecture:

typedef struct

void (∗function )( void ∗) ; t a sk co n t r o lb l ock { // Task entry point

void∗arg ; // Task parameters

uint8t ∗stackbase ; // Stack memory (96 bytes )

t a s k s t a t e t state ; // Current task s t a t e

uint16t s l e e p t i c k s ; // Sleep countdown

uint8t p r i o r i t y ; // Execution p r i o r i t y (0−3)

char name [TASKNAMELENGTH] ; // Task i d e n t i f i e r

} taskt ;

2.2 Task State Transitions

The system implements a finite state machine for task management:

TASKREADY⇀↽TASKRUNNING →TASKSLEEPING →TASKREADY

1

2.3 Task Creation Protocol

i n t 8 t taskcr eat e ( const char∗name , void (∗function )( void ∗) ,

void∗arg , uint8t priority , uint8t ∗s t a c k b u f f e r )

Creation Constraints:

• Maximum task count: MAXTASKS = 4

• Stack size: STACKSIZE = 96 bytes

• Priority levels: {PRIORITYIDLE, PRIORITYLOW, PRIORITYMEDIUM, PRIORITY

3 Scheduling Algorithm

3.1 Round-Robin Implementation

The scheduler employs a circular search algorithm to find the next executable task:

static

uint8t

uint8 tnexttask = ( c u r r e n t t a s k i d + 1) % MAXTASKS; get next task ( void ) {

for ( uint8t

i f ( i s t a s k v a l i d ( nexttask ) && i = 0; i < MAX TASKS; i++) {

return nexttask ; task table [ next task ] . state == TASK READY) {

} nexttask = ( nexttask + 1) % MAXTASKS;

} return c u r r e n t t a s ki d ;

}

3.2 Execution Flow

The main scheduler loop follows this sequence:

1. Enter critical section (disable interrupts)

2. Execute current task function

3. Calculate next task ID using round-robin

4. Leave critical section (enable interrupts)

5. Apply 1ms CPU delay to prevent overload

4 Memory Management

4.1 Resource Allocation

The system employs static memory allocation for predictable resource usage:

2

Total RAM for stacks = MAXTASKS × STACKSIZE = 4 × 96 = 384 bytes

TCB memory footprint = MAXTASKS × sizeof(taskt) ≈112 bytes

Global variables ≈20 bytes

Total estimated usage ≈516 bytes

4.2 Configuration Parameters

#define MAXTASKS 4 // Maximum concurrent tasks

#define STACKSIZE 96 // Bytes per task stack

#define TICKFREQUENCY 100 // Hz −scheduler frequency

#define TASKNAMELENGTH 8 // Maximum task name characters

5 Interrupt and Critical Section Management

5.1 Atomic Operation Protection

The kernel implements nested critical sections to protect shared resources:

void

c l i ( ) ; e n t e r c r i t i c a l s e c t i o n ( void ) { // Disable i n t e r r u p t s

c r i t i c a l n e s t i n g ++; // Track nesting depth

}

| void |

|

i n t e r r u p t s | |||

|---|---|---|---|---|---|

| i f | ( c r i t i c a l n e s t i n g == 0) | s e i ( ) ; |

|

}

5.2 Timer Interrupt Configuration

The system timer generates 100Hz interrupts for tick management:

OCR1A = Prescaler × Frequency−1 = 16, 000, 000−1 = 2499

// Timer1 configuration for 100Hz

TCCR1A = 0;

| TCCR1B = (1 << WGM12) | | | (1 << CS11) | | |

|

|---|---|---|---|---|

|

TIMSK1 |= (1 << OCIE1A) ;

6 Sleep and Timing Mechanisms

6.1 Tick-Based Sleep System

Tasks can suspend execution for precise durations using system ticks:

3

| slpicks= | milliseconds |

|---|---|

| slpicks= | 10 |

|

tasktable [ c u r r e n tt a s ki d ] . s l e e p t i c k s = t i c k s ; tasktable [ c u r r e n tt a s ki d ] . state = TASKSLEEPING; l e a v e c r i t i c a l s e c t i o n ( ) ;

schedule ( ) ;

}

6.2 Tick Update Algorithm

The interrupt service routine manages sleeping tasks:

ISR(TIMER1COMPAvect) { systemticks++;

for ( uint8t i f ( tasktable [ i ] . state == TASKSLEEPING && i = 0; i < MAX TASKS; i++) {

tasktable [ i ] . s l e e p t i c k s > 0) { tasktable [ i ] . s l e e p t i c k s −−;

i f ( tasktable [ i ] . s l e e p t i c k s == 0) { tasktable [ i ] . state = TASKREADY; }

}

}

}

7 System Initialization Sequence

7.1 Boot Process

1. Memory Zeroing: Clear task table and global variables

2. Timer Configuration: Setup 100Hz interrupt timer

3. Idle Task Creation: Initialize fallback task with lowest priority

4. Interrupt Enable: Start scheduler tick generation

5. Task Validation: Mark all created tasks as READY state

8 Error Handling and Robustness

8.1 Boundary Condition Management

• Task Validation: All task executions verify function pointer validity

4

• Sleep Sanitization: Zero-tick sleep requests default to 1 tick• Circular Search: Scheduler handles empty task tables gracefully• Nesting Safety: Critical sections properly handle nested calls

8.2 Recovery Mechanisms

static return ( taskid < MAX TASKS && task table [ taskid ] . function != NULL) ; uint8 t i s t a s k v a l i d ( uint8 t task id ) {

}

|

|

|---|

|

Time Complexity | Space Complexity |

|---|---|---|

|

|

|

Table 1: Algorithm Complexity Analysis

9.2 Memory Efficiency

The system achieves high memory efficiency through:• Static allocation eliminating heap fragmentation• Fixed-size arrays for predictable memory usage• Stack sharing between kernel and application• Minimal TCB overhead (28 bytes per task)

10 Build System Integration

10.1 Compilation Configuration

MCU = atmega328p

FCPU = 16000000UL

CFLAGS = −mmcu=$ (MCU) −DFCPU=$ (FCPU) −Os −Wall −std=c99

10.2 Memory Section Allocation

Program Memory = .text + .data

RAM Usage = .data + .bss + Stack

5